## CW12D1800 Data Sheet

# **Dual Channel 12-bit, 1.8 GSPS High Speed ADC**

#### 1.Overview

The CW12D1800 is a 12-bit high-speed ADC product with two built-in 12-Bits.

1.8 GSPS high-speed ADC, each channel ADC has independent DDR data clocks (DCLKI and DCLKQ). When both channel ADC are operating, DCLKI and DCLKQ are always in phase, so only one of them can be used to collect all data. If 1:2 Demux mode is selected, another set of 12-Bit LVDS buses are enabled so that the data rate of each set of LVDS changes to 1/2 of the Non-Demux mode to reduce the timing requirements for data capture.

The CW12D1800 supports AutoSync function and can be used for multi-chip cascade. The product package is plastic-sealed BGA292 package, with an operating temperature of -  $55^{\circ}$ C  $\sim 105^{\circ}$ C. The CW12D1800 achieves excellent dynamic performance with low power consumption below 2.4W.

The data output format of the CW12D1800 can be programmed to offset binary code and complement code, and output data using an LVDS interface that complies with international common standards. The output common mode can be adjusted at two voltages: 0.8V and 1.2V. CW12D1800 and CW12D1600/ CW12D1000/CW10D1500/

#### 2 Applications

CW10D1000 pin compatible.

- RF direct down-conversion

- High-speed data acquisition system

- Ultra-wideband satellite data reception

- Automatic test equipment

- High-speed test instrument

- Wideband radar

- Electronic countermeasures

#### 3 Features

- Built-in dual-channel 1.8 GSPS ADC

- Low power consumption, no heat sink required

- Built-in terminal resistor (automatic calibration), buffer

- Provides test sequences for system debugging and batch testing

- 1:1 Non-Demux or 1:2 Demux LVDS data output

- Multi-chip automatic synchronization function

- Single power supply 1.9 V

- 292-BGA (27mm × 27mm × 1.7mm, 1.27mm ball spacing)

- Pin and

CW12D1600/CW12D1000/CW10D1500/CW10D1000

compatible

#### 4 Performance indicators

- Full power bandwidth: 3.0 GHz

- Data delay: 28 master clock cycles

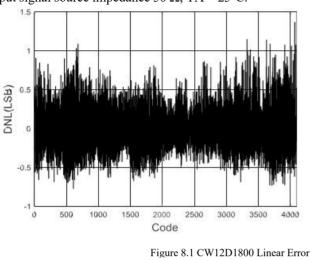

- Static performance: DNL -0.9/+1.5 LSB, INL -2.3/+2.8 LSB

- Dynamic performance (fs = 1.8 GSPS, input signal power 1 dBFS)

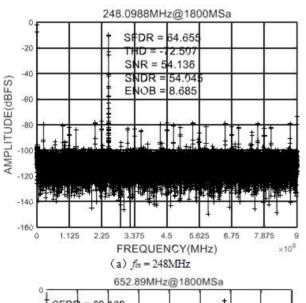

- fin=248MHz ENOB = 8.7 Bit, SFDR = 64.7 dBFS, SNR = 54.1 dBFS

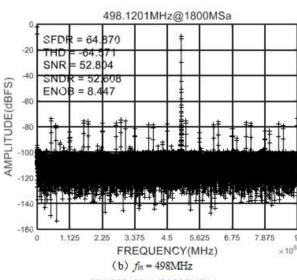

- fin=498MHzENOB = 8.5 Bit, SFDR = 64.8 dBFS, SNR = 52.8 dBFS

- fin = 998 MHz ENOB = 8.0 Bit, SFDR = 60.1 dBFS, SNR = 49.9 dBFS

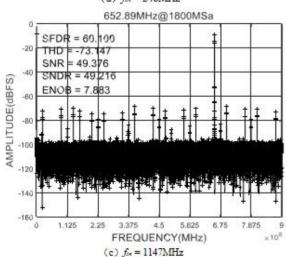

- fin=1147 MHzENOB = 7.9 Bit, SFDR = 60.1 dBFS, SNR = 49.4 dBFS

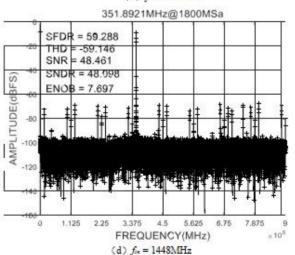

- fin=1448 MHzENOB = 7.7 Bit, SFDR = 59.3 dBFS, SNR = 48.5 dBFS

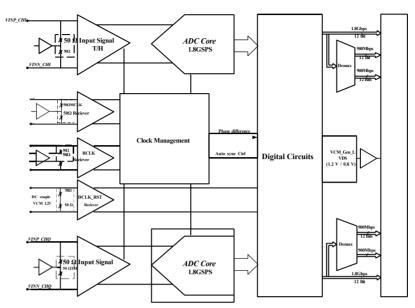

# 5 Simplified block diagram

Figure 5.1 CW12D1800 system block diagram

# **6** Typical Performance

Table 6-1 Chip usage conditions

| Parameter                                        | Symbol                              | Comments                                           | Value                       | Units |

|--------------------------------------------------|-------------------------------------|----------------------------------------------------|-----------------------------|-------|

|                                                  | $V_{A}$                             | Analog circuit power supply                        | 1.9                         | V     |

| Power supply voltage                             | $V_{TC}$                            | Sample hold and clock circuit power supply         | 1.9                         | V     |

|                                                  | $V_{ m DR}$                         | Output driver circuit power supply                 | 1.9                         | V     |

|                                                  | $V_{\rm E}$                         | Digital circuit power supply                       | 1.9                         | V     |

| Power-on sequence                                |                                     | No power-on sequence requirement                   |                             |       |

|                                                  | GND                                 | Analog circuit ground                              | 0                           | V     |

| Ground                                           | $GND_{TC}$                          | Sample hold and clock circuit ground               | 0                           | V     |

|                                                  | $GND_{DR}$                          | Output driver circuit ground                       | 0                           | V     |

|                                                  | $GND_E$                             | Digital circuit ground                             | 0                           | V     |

| Differential input<br>analog signal<br>amplitude | VinIp –VinIn<br>VinQp –VinQn        | Channel analog input signal differential amplitude | 800                         | mVpp  |

| Logic input high level                           | $V_{\rm I}$                         |                                                    | VA                          | V     |

| Logic input low level                            | $V_{IL}$                            |                                                    | GND                         |       |

| Clock differential input signal amplitude        | $V_{\text{CLKP}} - V_{\text{CLKN}}$ | Clock input signal differential amplitude          | 600                         | mVpp  |

| Clock frequency                                  | $ m f_{CLK}$                        |                                                    | $0.5 \le f_{CLK} \le 1.8$   | GHz   |

| Operating temperature range                      | $T_{\rm C}$                         |                                                    | $-55 \le T_{\rm C} \le 105$ | °C    |

Table 6-2 Thermal resistance parameters

| parameter                                                          | symbol          | Typical values | unit |

|--------------------------------------------------------------------|-----------------|----------------|------|

| Thermal resistance between the junction and the environment        | $R_{\theta JA}$ | 22.9           | °C/W |

| Thermal resistance between the junction and the top of the package | $R_{	heta JC}$  | 7.7            | °C/W |

| Thermal resistance between the junction and the circuit board      | $R_{\theta JB}$ | 17.9           | °C/W |

E-mail: sales @ cdcwtec.com

Table 6-3 Electrical characteristics of power supply, input and output

The chip operates in Demux and Non-DES modes, and  $V_A = V_{DR} = V_{TC} = V_E = +1.9V$ , AC coupled signal input, unused channel termination is connected to "AC ground", AC coupled sine wave sampling clock,  $f_{CLK} = 1.8$  GHz;  $R_{ext} = R_{trim} = 3300 \ \Omega \pm 0.1\%$ ; input source impedance 50  $\Omega$ ; TA = 25 °C.

| parameter                                           | symbol        | Minimum | value Typical | values Maximum value | unit |

|-----------------------------------------------------|---------------|---------|---------------|----------------------|------|

| Resolution                                          |               |         | 12            | !                    |      |

| Power supply voltage:                               |               |         |               |                      |      |

| Analog circuit power supply                         | $V_{A}$       | 1.8     | 1.9           | 2.0                  | V    |

| Sampling and holding<br>and clock circuit<br>source | $V_{TC}$      | 1.8     | 1.9           | 2.0                  | V    |

| Output drive circuit                                | $V_{DR}$      | 1.8     | 1.9           | 2.0                  | V    |

| power supply                                        |               |         |               |                      |      |

| Digital circuit power supply                        | $V_{E}$       | 1.8     | 1.9           | 2.0                  | V    |

| Power supply current:                               |               |         |               |                      |      |

| Analog circuit power supply                         | $I_A$         |         | 19            |                      | mA   |

| Sampling and holding<br>and clock circuit<br>source | $I_{TC}$      |         | 68            | 0                    | mA   |

| Output drive circuit power supply                   | $I_{DR}$      |         | 370           | 0                    | mA   |

| Digital circuit power supply                        | $I_{\rm E}$   |         | 18.           | 5                    | mA   |

| Power consumption                                   |               |         |               |                      |      |

| PDI = PDQ = GND                                     | <u> </u>      |         | 2.3           | 8                    | W    |

| $PDI = GND, PDQ = V_A$                              | $P_{D}$       |         | 1.2           |                      | W    |

| $PDI = V_A, PDQ = GND$                              | гD            |         | 1.2           | 2                    | W    |

| $PDI = V_A, PDQ = V_A$                              |               |         | 1.9           | )                    | mW   |

|                                                     |               | Da      | ata input     |                      |      |

| Input differential analog                           | VinIp – VinIn |         | 80            | 0                    | mVpp |

| signal amplitude                                    | VinQp – VinQn |         | 80            | 0                    | mVpp |

| Differential input resistance                       | $R_{ m IN}$   | 95      | 10            | 0 105                | Ω    |

E-mail: sales @ cdcwtec.com

Table 6-4 Electrical characteristics of power supply, input and output (continued)

| Pa               | rameter                     | Symbol                                | Minimum value     | Typical value      | Maximum value    | Unit                    |

|------------------|-----------------------------|---------------------------------------|-------------------|--------------------|------------------|-------------------------|

|                  |                             |                                       | Clock in          | put                |                  |                         |

| Clock            | source type                 |                                       |                   |                    |                  | Different ial sine wave |

| _                | out differential<br>swing   | V <sub>CLKP</sub> – V <sub>CLKN</sub> | 400               | 600                | 1000             | mVpp                    |

|                  | fferential input sistance   | $R_{CLK}$                             | 95                | 100                | 105              | Ω                       |

|                  | al clock jitter<br>uirement | Jitter                                |                   |                    | 100              | fs                      |

|                  | duty cycle<br>uirement      | Duty Cycle                            | 40                | 50                 | 60               | %                       |

|                  |                             | N                                     | Iulti-chip DCLK_R | ST Sync signal     |                  |                         |

| Logic            | compatibility               |                                       |                   | LVDS               |                  |                         |

| Input            | voltage:                    |                                       |                   |                    |                  |                         |

| Logic            | low                         | $V_{IL\_DRST}$                        |                   |                    | 1.1              | V                       |

| Logic            | high                        | $V_{IH\_DRST}$                        | 1.3               |                    |                  | V                       |

| S                | Swing                       | $V_{ID\_DRST}$                        |                   | 350                |                  | mV                      |

| Common           | -mode voltage               | $V_{CM\_DRST}$                        |                   | 1.20               |                  | V                       |

| Input resistance |                             | $R_{DRST}$                            | 95                | 100                | 105              | Ω                       |

|                  |                             | Mul                                   | ti-chip RCLK sync | hronization signal |                  |                         |

| Logic c          | ompatibility                |                                       |                   | LVDS               |                  |                         |

| Input            | voltage:                    |                                       |                   |                    |                  |                         |

| Logic            | low                         | $V_{\rm IL\_RCLK}$                    |                   |                    | 1.1              | V                       |

| Logic            | high                        | $V_{\mathrm{IH\_RCLK}}$               | 1.3               |                    |                  | V                       |

| S                | Swing                       | $V_{\text{ID\_RCLK}}$                 |                   | 350                |                  | mV                      |

| Common           | -mode voltage               | $V_{\text{CM\_RCLK}}$                 |                   | 1.20               |                  | V                       |

| Input            | resistance                  | R <sub>RCLK</sub>                     | 95                | 100                | 105              | Ω                       |

|                  |                             |                                       | SPI               |                    |                  |                         |

| Low-leve         | l input voltage             | $V_{IL\_SPI}$                         | 0                 |                    | $0.3 \times V_A$ | V                       |

| High-leve        | el input voltage            | $V_{\mathrm{IH\_SPI}}$                | $0.7 \times V_A$  |                    | $V_{A}$          | V                       |

|                  | output voltage              | $V_{\mathrm{OL\_SPI}}$                |                   |                    | 0.3              | V                       |

|                  | l output voltage            | $V_{\mathrm{OH\_SPI}}$                | 1.6               |                    |                  | V                       |

| Serial clo       | ock frequency               | $f_{\mathrm{SCLK}}$                   |                   |                    | 10               | MHz                     |

| Logic compatibility              |                  |     | LVDS    |     |                       |

|----------------------------------|------------------|-----|---------|-----|-----------------------|

| Swing (single-sided)             | $V_{OD}$         | 300 | 350     | 400 | mVpp                  |

| Common-mode voltage              | $V_{CM\_LVDS}$   |     | 1.2/0.8 |     | V                     |

| Output data delay                | $t_{\rm LAT}$    |     | 28      |     | Sampling clock period |

| Data output rising edge (20 pF)  | $t_{ m LHT}$     |     | 220     |     | ps                    |

| Data output falling edge (20 pF) | t <sub>HLT</sub> |     | 220     |     | ps                    |

| Clock data output<br>deviation   | $t_{\rm OSK}$    | 180 |         | 350 | ps                    |

| Clock data setup time (90°)      | t <sub>SU</sub>  |     | 350     |     | ps                    |

| Clock data hold time (90°)       | $t_{\mathrm{H}}$ |     | 400     |     | ps                    |

Table 6-5 Static characteristics

| Parameter                                | Symbol    | Minimum | Typical | Maximum | Unit |

|------------------------------------------|-----------|---------|---------|---------|------|

|                                          |           |         |         |         |      |

| Differential nonlinearity                | DNL       | -0.84   |         | 1.16    | LSB  |

| Integral nonlinearity                    | INL       | -2.54   |         | 2.85    | LSB  |

| Output offset error<br>(offset<br>error) | VOS       |         | 8       |         | LSB  |

| Full scale error (full scale error)      | PFSE/NFSE |         | ±15     |         | mV   |

Table 6-6 Dynamic characteristics

| Parameter                      |                | Symbol       | Minimum | Typical | Maximum | Unit         |

|--------------------------------|----------------|--------------|---------|---------|---------|--------------|

| Full power bands               | width:         | FPBW         |         | 3.0     |         | GHz          |

| fs = 1.8 GSPS, V               | /in = -1 dBFS  |              |         |         |         |              |

|                                | fin = 248  MHz |              |         | 8.7     |         | bit          |

|                                | fin = 498 MHz  |              |         | 8.4     |         | bit          |

|                                | fin = 998 MHz  | ENOB         |         | 8.0     |         | bit          |

| Effective number of bits       | fin = 1147 MHz |              |         | 7.9     |         | bit          |

| number of bits                 | fin = 1448 MHz |              |         | 7.7     |         | bit          |

|                                | fin = 248 MHz  |              |         | 54.1    |         | dBFS         |

|                                | fin = 498 MHz  |              |         | 52.6    |         | dBFS         |

|                                | fin = 998 MHz  | SNDR         |         | 49.8    |         | dBFS         |

| Signal to Noise and Distortion | fin = 1147 MHz |              |         | 49.2    |         | dBFS         |

| Ratio                          | fin = 1448 MHz |              |         | 48.1    |         | dBFS         |

|                                | fin = 248  MHz |              |         | 54.1    |         | dBFS         |

|                                | fin = 498 MHz  |              |         | 52.8    |         | dBFS         |

|                                | fin = 998 MHz  |              |         | 49.9    |         | dBFS         |

| Signal to Noise<br>Ratio       | fin = 1147 MHz | SNR          |         | 49.4    |         | dBFS         |

| Katio                          | fin = 1448 MHz |              |         | 48.5    |         | dBFS         |

|                                | fin = 248 MHz  |              |         | 70.8    |         | dBFS         |

|                                | fin = 498 MHz  |              |         | 64.7    |         | dBFS         |

| m . 1                          | fin = 998 MHz  | THD          |         | 65.8    |         | dBFS         |

| Total<br>Harmonic              | fin = 1147 MHz |              |         | 63.8    |         | dBFS         |

| Distortion                     | fin = 1448 MHz |              |         | 59.1    |         | dBFS         |

|                                | fin = 248 MHz  |              |         | 64.7    |         | dBFS         |

|                                | fin = 498 MHz  |              |         | 64.8    |         | dBFS         |

|                                | fin = 998 MHz  | SFDR         |         | 60.1    |         | dBFS         |

| Spurious Free Dynamic          | fin = 1147 MHz |              |         | 60.1    |         | dBFS         |

| Range                          | fin = 1448 MHz |              |         | 59.3    |         | dBFS         |

|                                | fin = 248 MHz  |              |         | 79.3    |         | dBFS         |

|                                | fin = 498 MHz  |              |         | 83.1    |         | dBFS         |

|                                | fin = 998 MHz  |              |         | 82.7    |         | dBFS         |

| Second Harm                    | fin = 1147 MHz | 2nd<br> Harm |         | 82.8    |         | dBFS         |

|                                | fin = 1448 MHz | 1133111      |         | 76.7    |         | dBFS         |

|                                | fin = 248 MHz  |              |         | 83.2    |         | dBFS         |

|                                | fin = 498 MHz  |              |         | 74.5    |         | dBFS         |

| gg( ' 177                      | fin = 998 MHz  | 12. 1        |         | 75.4    |         | dBFS         |

| Third Harm                     | fin = 1147 MHz | 3rd<br> Harm |         | 70.6    |         | dBFS         |

|                                | fin = 1448 MHz | 1141111      |         | 67.5    |         | dBFS         |

|                                |                |              |         | - U     |         | Page 7 of 26 |

Page 7 of 26

Table 6-7 Calibration characteristics

| Parameter              | Symbol                | Minimum | Typical             | Maximum | Unit                  |

|------------------------|-----------------------|---------|---------------------|---------|-----------------------|

|                        |                       |         |                     |         |                       |

| Calibration period     | t <sub>CAL</sub>      |         | 8 × 10 <sup>5</sup> |         | Sampling clock period |

| Calibration low time   | $t_{\mathrm{CAL\_L}}$ | 1000(1) |                     |         | Sampling clock period |

| Calibration high time  | t <sub>CAL_H</sub>    | 1000(1) |                     |         | Sampling clock period |

| Calibration delay time | t <sub>CalDly</sub>   |         | 1600                |         | Sampling clock period |

# 7 Pin configuration and function description

|   | 1             | 2             | 3       | 4            | 5      | 6            | 7            | 8     | 9     | 10    | 11     | 12     | 13      | и       | 15    | 16      | 17     | 18     | 19      | 20      |   |

|---|---------------|---------------|---------|--------------|--------|--------------|--------------|-------|-------|-------|--------|--------|---------|---------|-------|---------|--------|--------|---------|---------|---|

| Α | CND           | V_A           | 500     | TFM          | NDM    | V_A          | CIND         | V_E   | GND_E | DidOp | V_DR   | Did3p  | GND_DR  | Diditip | V_DR  | Didip   | GND_DR | Did11p | Dk#11n  | OND_DR  | ٨ |

| В | VCM_<br>LVDS  | GND           | ECEb    | SDI          | CalRun | V,A          | GND          | GND_E | V.E   | Did0n | Dkd2p  | Did3n  | Did5p   | Did8n   | Did8p | Did9n   | Did10p | DIOp   | Olip    | Ditin   | В |

| С | Rtrimp        | DC_AC         | Redp    | 90%          | SCLK   | V,A          | NC.          | V.E   | GND_E | Did1p | Dkd2n  | Dl64p  | Did5n   | Dld7p   | Did8n | Old10n  | Dión   | V_DR   | OEÞ     | Di2n    | С |

| D | DINC          | Rhimn         | Redn    | GND          | GND    | CAL          | DNC          | V,A   | V,A   | Did1n | V_DR   | Dld4n  | GND DR  | Dlo7n   | V_DR  | GND DR  | V.DR   | DiSp   | D14p    | DI4n    | D |

| Ε | V_A           | Tdiodep       | DNC     | GND          |        |              |              |       |       |       |        |        |         |         |       |         | GND_DR | DIBn   | DISp    | Diffn   | E |

| F | :V_A          | GND_TC        | Tdioden | DNC          |        |              |              |       |       |       |        |        |         |         |       |         | GND_DR | DIEp   | Diffin  | GND_DR  | F |

| G | V_TC          | GND_TC        | V_TC    | V_TC         |        |              |              |       |       |       |        |        |         |         |       |         | DI7p   | DI7n   | Diffic  | DiBn    | G |

| н | Virip         | V_TC          | GND_TC  | V.A          |        |              | ,            | GND   | GND   | GND   | GND    | GND    | GND     | S.      |       |         | DI9p   | DI9n   | D(10p   | Di10n   | н |

| J | Vinin         | GND_TC        | V_TC    | TE_<br>VREFT |        |              |              | GND   | GND   | GND   | GND    | GND    | GND     | 60      |       |         | V_DR   | DITTP  | Ditte   | V_DR    | 1 |

| К | GND           | TE_<br>VREFT  | V_TC    | GND_TC       |        |              |              | GND   | GND   | GND   | GND    | GND    | GND     |         |       |         | ORlp   | ORIn   | DCLK_lp | DCLK_In | к |

| L | CND           | TE_<br>VREFB  | V_TC    | GND_TC       |        |              |              | GND   | CAND  | GND   | GND    | OND    | GND     | 0       |       |         | ORQp   | ORQn   | DCLK_Qp | DCLK_Qn | L |

| м | VinQn         | GND_TC        | V_TC    | TE_<br>VREFB |        |              |              | GND   | CND   | GND   | GNO    | GND    | GND     | 300     |       |         | GND_DR | DQ11p  | DQ11n   | GND_DR  | М |

| N | VinQp         | V_TC          | GND_TC  | V.A          |        |              |              | GND   | GND   | GN0   | GND    | GND    | GND     | et v    |       |         | DQ9p   | DQ9n   | DQ10p   | DQ10n   | N |

| Р | V TC          | GND_TC        | v_tc    | V_TC         |        |              |              |       |       |       |        |        |         | ž.      |       |         | DQ7p   | DQ7n   | DQ8p    | DOBn    | р |

| R | V_A           | GND_TC        | V_TC    | у_тс         |        |              |              |       |       |       |        |        |         |         |       |         | V_DR   | D06p   | DQ6n    | V DR    | R |

| т | V_A           | GND_TC        | GND_TC  | GND          |        |              |              |       |       |       |        |        |         |         |       |         | V_DR   | DQ9n   | DQ5p    | DQ5n    | т |

| U | GND_TC        | СКр           | POI     | GND          | GND    | ROOUT<br>_tn | DNC          | V_A   | V_A   | DQdfn | V_DR   | DQrHn  | GND_DR  | DQrj7n  | V_DR  | V_DR    | GND_DR | D03p   | DQ4p    | DQ4n    | U |

| ٧ | CLKn          | DOLK<br>_RSTp | PDQ     | CalDiy       | DES    | ROOUT<br>_2p | RCOUT<br>_2h | V_E   | GND_E | DQdfp | DQtf2h | DOdAp  | DQd5n   | DQd7p   | DQd8n | DQdft0n | DQX0H  | GND_DR | DG2p    | DQ2n    | v |

| W | DCUK<br>_RSTn | GND           | DNC     | DORPh        | ROUKn  | V.A          | GND          | GND_E | V.E   | DGd0n | DQd2p  | DQd3n  | DiGatip | DQd6n   | DGdBp | DQd9n   | DQd10p | DOOp   | DQfp    | DQ1n    | w |

| Y | GND           | V_A           | FSR     | RCLKp        | RCOUT  | V_A          | GND          | V_E   | GND_E | DGdBp | V_DR   | DQxl3p | GND_DR  | DQdSp   | V_DR  | DQd9p   | GND_DR | DQd11p | DQd11n  | GND_DR  | ٧ |

|   | 1             | 2             | 3       | 4            | 5      | 6            | 7            | 8     | 9     | 10    | 11     | 12     | 13      | 54      | 15    | 18      | 17     | 18     | 19      | 20      |   |

Figure 7.1 Pin Configuration of CW12D1800 (Top View)

Table 7-1 Pin function description

| Pin number             | Symbol                               | Function                                                                  |

|------------------------|--------------------------------------|---------------------------------------------------------------------------|

| H1, J1                 | Vinlp, VinIn                         | 1/0 1 11:00 4:1: 1: 4:                                                    |

| N1, M1                 | VinQp, VinQn                         | I/Q channel differential signal input                                     |

| U2, V1                 | CLKp, CLKn                           | Differential sampling clock signal input                                  |

| V2, W1                 | DCLK_RSTp, DCLK_RSTn                 | Differential clock reset. Positive pulse reset DCLKI and DCLKQ output     |

| C2                     | DC_AC                                | AC Couple selection port, chip internal default pull-down                 |

| B1                     | VCM_LVDS                             | LVDS output VCM Select, the chip defaults to pull-up                      |

| E2, F3                 | Tdiodep, Tdioden                     | Temperature sensor diode positive and negative ports                      |

| J4, K2                 | TE_VREFT                             | REFT channel test output                                                  |

| L2, M4                 | TE_VREFB                             | REFB channel test output                                                  |

| D1, D7, E3, F4, W3, U7 | DNC                                  | Floating pin, cannot be connected to any potential                        |

| C7                     | NC                                   | Null pin                                                                  |

| C3, D3                 | Rextp, Rextn                         | External 3.3kΩ precision resistor port 1                                  |

| C1, D2                 | Rtrimp, Rtrimn                       | External 3.3kΩ precision resistor port 2                                  |

| Y4, W5                 | RCLKp, RCLKn                         | Synchronous reference clock input                                         |

| Y5, U6<br>V6, V7       | RCOut1p, RCOut1n<br>RCOut2p, RCOut2n | Reference clock output 1 and output 2                                     |

|                        |                                      | Double-edge sampling mode selection, when the                             |

|                        |                                      | input is set to logic high, DES (Double Edge                              |

|                        |                                      | Sample) operating mode is selected, which means                           |

|                        |                                      | sampling the I-channel and Q-channel inputs in a                          |

| 175                    | DEC                                  | time interleaving manner. When this input is set to                       |

| V5                     | DES                                  | logic low, the chip is in Non-DES operating mode,                         |

|                        |                                      | i.e., the I channel and Q channel operate                                 |

|                        |                                      | -                                                                         |

|                        |                                      | independently. In Extended Control Mode (ECM,                             |

|                        |                                      | Extended Control Mode), this input is ignored, and                        |

|                        |                                      | the DES mode selection is controlled by the DES                           |

|                        |                                      | bit (address: 0h, bit 7) through the control register;                    |

|                        |                                      | the default is Non-DES mode operation. Internal                           |

|                        |                                      | chip silent Recognize pull down.                                          |

| V4                     | CalDly                               | Calibration delay selection, the internal chip is pulled down by default. |

|          |            | Calibration initialization. The user can have the chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |            | perform self-calibration by keeping the input high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |            | at least tCAL_H after keeping the input low at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D.       | CAL        | least tCAL_L. If this input remains high on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D6       | CAL        | power-on, automatic power-on calibration will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |            | disabled. This pin is valid in both ECM and Non-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |            | ECM. In ECM, this pin is logical or operational                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |            | with the CAL bit (address: 0h, bit 15) in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |            | control register. Therefore, both pins and bits must                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |            | be set to low and then either one mustbesettohigh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |            | toperform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |            | Command calibration. The chip internal drop-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |            | down is pulled down by default.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B5       | CalRun     | Calibration flag output, this output is logically high power when performing the calibration process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |            | flat. Otherwise this output is logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| U3<br>V3 | PDI<br>PDQ | I/Q channel shutdown control. Setting any input to logic high will turn off Close the corresponding I or Q channel. Set either input to logic low Will cause the corresponding I or Q channels to enter the working state after a certain time delay state. This pin is valid in both ECM and Non- ECM. In ECM In this case, each pin performs logic or operation with its respective bits. Therefore, no Whether this pin or the PDI and PDQ bits in the control register are available Used to close I and Q channels respectively (address: 0h, bit 11 and bit 10). The chip internal drop-down is pulled down by default. |

| A4       | TPM        | Test mode selection, when the input is logic high, the chip continuouslyoutputs a set of repeated fixed digital sequences. In ECM, this input is ignored, and the test mode can only control the register TPM bits (address: 0h, bit 12) control. The chip internal drop-down is pulled down by default.                                                                                                                                                                                                                                                                                                                      |

| Non-Demux mode selection, setting this input to logic high will set the digital output bus to 1:1 Non-Demuxed |

|---------------------------------------------------------------------------------------------------------------|

|                                                                                                               |

| digital output bus to 1:1 Man Damuyad                                                                         |

| digital output ous to 1.1 Non-Demuxed                                                                         |

| mode. Setting this input to logic low                                                                         |

| will set the digital output bus to 1:2                                                                        |

| Demuxed mode. This function is only controlled                                                                |

| by pins and in ECM and                                                                                        |

| Stay active during Non-ECM. The chip internal                                                                 |

| drop-down is pulled down by default.                                                                          |

|                                                                                                               |

| Full scale input range selection. In Non-ECM,                                                                 |

| this input must be set to logic high; the full-                                                               |

| scale differential input range for the I and Q                                                                |

| channel inputs is set by this pin. In ECM, this                                                               |

| input is ignored, and the full scale range of I                                                               |

| and Q channel inputs is set by Addr:3h and                                                                    |

| Addr:Bh, respectively.                                                                                        |

| Set to determine independently. The chip is                                                                   |

| pulled up by default.                                                                                         |

|                                                                                                               |

| DDR phase selection. This input selects the                                                                   |

| 0°Data- to-DCLK phase relationship when the                                                                   |

| logic is low. When logic is high, it selects the                                                              |

| 90°Data-to- DCLK phase relationship, i.e. the                                                                 |

| DCLK conversion indicates the middle of the valid                                                             |

| data output. This pin is only valid when the chip is                                                          |

| in 1:2 Demux mode, i.e. the NDM pin is set to                                                                 |

| logic low. In ECM, this input is ignored and the                                                              |

| DDR phase is passed by the DPS bit (address: 0h,                                                              |

| bit 14)                                                                                                       |

| Control register selection; default is 0° mode. The chip                                                      |

| internal drop-down is pulled down by default.                                                                 |

| Extended control enable. When this signal is                                                                  |

| valid (logic low), the extended function control is                                                           |

| performed through the SPI interface. In this case,                                                            |

| most direct control pins do not work. When the                                                                |

| signal is invalid (logic high), the SPI interface is                                                          |

| disabled and all SPI registers are reset to their                                                             |

| default values. All available settings are controlled                                                         |

|                                                                                                               |

| via the control pin. The chip is pulled up by default.                                                        |

|                                                                                                               |

| C4                                                                                    | SCSb | SPI chip selection, the internal chip is pulled up by default.                    |

|---------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------|

| C5                                                                                    | SCLK | SPI serial clock, the chip internal drive is pulled down by default.              |

| B4                                                                                    | SDI  | SPI serial data input, the chip internal drop-<br>down is pulled down by default. |

| A3                                                                                    | SDO  | SPI serial data output                                                            |

| A2, A6, B6, C6, D8, D9,<br>E1, F1,<br>H4, N4, R1, T1,<br>U8, U9, W6, Y2, Y6           | V_A  | Analog circuit power supply                                                       |

| G1, G3, G4, H2 J3,<br>K3, L3, M3 N2,<br>P1, P3, P4<br>R3, R4                          | V_TC | Sampling and hold and clock circuit power supply                                  |

| A11, A15, C18 D11, D15,<br>D17<br>J17, J20, R17 R20, T17,<br>U11 U15, U16, Y11<br>Y15 | V_DR | Output Driver power                                                               |

Table 7-1 Pin Function Description (continued)

| Terminal number                                                                                             | symbol                                                                                                                                  | Function                                   |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| A8, B9, C8, V8 W9, Y8                                                                                       | V_E                                                                                                                                     | Digital encoding circuit power supply      |

| A1, A7, B2, B7 D4, D5, E4,<br>K1 L1, T4, U4, U5 W2, W7,<br>Y1, Y7<br>H8:N13                                 | GND                                                                                                                                     | Analog circuit ground                      |

| F2, G2, H3, J2 K4, L4, M2,<br>N3 P2, R2, T2, T3<br>U1                                                       | GND_TC                                                                                                                                  | Sample and Hold and Clock Circuitry Ground |

| A13, A17, A20                                                                                               | GND_DR                                                                                                                                  |                                            |

| D13, D16, E17<br>F17, F20, M17<br>M20, U13, U17 V18, Y13,<br>Y17 Y20                                        |                                                                                                                                         | Output Driver Ground                       |

| A9, B8, C9, V9 W8, Y9                                                                                       | GND_E                                                                                                                                   | Digital encoding circuit ground            |

| K19, K20<br>L19, L20                                                                                        | DCLKIp, DCLKIn<br>DCLKQp, DCLKQn                                                                                                        | I/Q channel data clock LVDS output         |

| K17, K18<br>L17, L18                                                                                        | ORIp,ORIn<br>ORQp,ORQn                                                                                                                  | I/Q channel overrange LVDS output          |

| J18, J19 H19, H20 H17, H18 G19, G20 G17, G18 F18, F19 E19, E20 D19, D20 D18, E18 C19, C20 B19, B20 B18, C17 | DQ11p, DQ11n DQ10p, DQ10n DQ9p, DQ9n DQ8p, DQ8n DQ7p, DQ7n DQ6p, DQ6n DQ5p, DQ5n DQ4p, DQ4n DQ3p, DQ3n DQ2p, DQ2n DQ1p, DQ1n DQ0p, DQ0n | I/Q channel data LVDS output               |

Table 7-1 Pin Function Description (Continued)

| M18, M19             | DQ11p, DQ11n                    |                                      |

|----------------------|---------------------------------|--------------------------------------|

| N19, N20             | DQ10p, DQ10n                    |                                      |

| N17, N18             | DQ9p, DQ9n                      |                                      |

| P19, P20             | DQ8p, DQ8n                      |                                      |

| P17, P18             | DQ7p, DQ7n                      |                                      |

| R18, R19             | DQ6p, DQ6n                      | 7/0.1 11 TTP9                        |

| T19, T20             | DQ5p, DQ5n                      | I/Q channel data LVDS output         |

| U19, U20             | DQ4p, DQ4n                      |                                      |

| U18, T18             | DQ3p, DQ3n                      |                                      |

| V19, V20             | DQ2p, DQ2n                      |                                      |

| W19, W20             | DQ1p, DQ1n                      |                                      |

|                      |                                 |                                      |

| W18, V17             | DQ0p, DQ0n                      |                                      |

|                      |                                 |                                      |

|                      |                                 |                                      |

| Pin Number           | Symbol                          | Function                             |

| A18, A19             | DId11p, DId11n<br>DId10p,DId10n |                                      |

| B17, C16<br>A16, B16 | DId9p, DId9n                    |                                      |

| B15, C15             | DId8p,DId8n                     |                                      |

| C14, D14             | DId7p, DId7n                    |                                      |

| A14, B14             | DId6p,DId6n                     |                                      |

| B13, C13             | DId5p, DId5n                    |                                      |

| C12, D12<br>A12, B12 | DId4p,DId4n                     |                                      |

| B11, C11             | DId3p, DId3n                    |                                      |

| C10, D10             | DId2p,DId2n<br>DId1p, DId1n     |                                      |

| A10, B10             | DId1p, DId1n<br>DId0p, DId0n    |                                      |

|                      |                                 |                                      |

|                      |                                 | I/Q Channel data delay LVDS output   |

| Y18, Y19             | DQdllp, DQdlln                  | 1 Q Chainer data detay L v D3 output |

| W17, V16             | DQd11p, DQd11n<br>DQd10p,DQd10n |                                      |

| Y16, W16             | DQd9p, DQd9n                    |                                      |

| W15, V15             | DQd8p, DQd8n                    |                                      |

| V14, U14             | DQd7p,DQd7n                     |                                      |

| Y14, W14<br>W13, V13 | DQd6p, DQd6n                    |                                      |

| V12, U12             | DQd5p, DQd5n<br>DQd4p,DQd4n     |                                      |

| Y12, W12             | DQd3p, DQd3n                    |                                      |

| W11, V11             | DQd2p, DQd2n                    |                                      |

| V10, U10             | DQd1p,DQd1n                     |                                      |

| Y10, W10             | DQd0p, DQd0n                    |                                      |

|                      |                                 |                                      |

|                      |                                 |                                      |

## 8 Typical performance test curve

Chip works at Demux and Non-DES mode, and VA = VDR = VTC = VE = +1.9V, AC-coupled signal input, unused channels terminated to "AC ground", AC-coupled sine wave sampling clock, fCLK = 1.8 GHz; Rext = Rtrim = 3300  $\Omega \pm$ 0.1%; input signal source impedance 50  $\Omega$ ; TA = 25°C.

INL(LSB) Code

Figure 8.2 Dynamic Characteristics of CW12D1800D (FS=1.8GHz)

Page 16 of 26

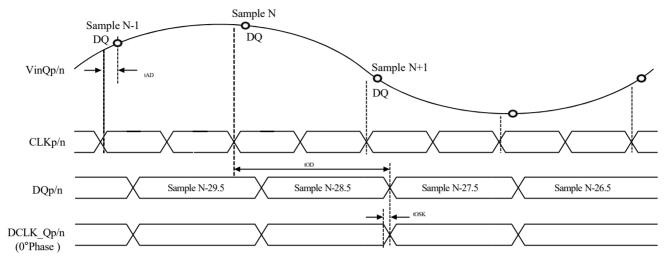

## 9 Timing diagram

## 1. Data timing

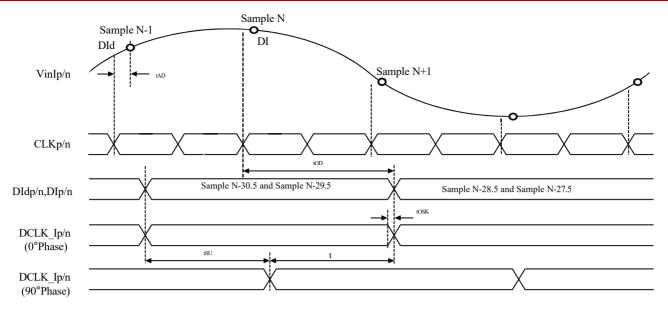

Figure 9.1 CW12D1800 data timing in Non-Demux Non-DES mode

#### **Description:**

The I channel data timing is exactly the same as the Q channel.

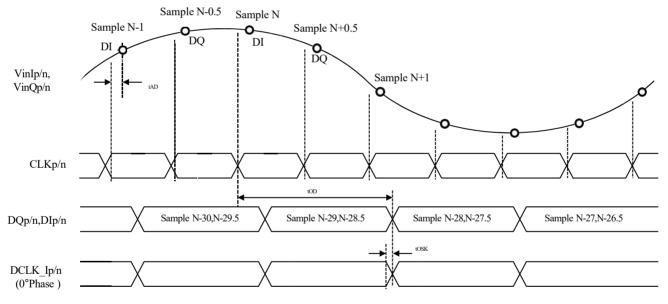

Figure 9.2 CW12D1800 data timing in Non-Demux DES mode

#### **Description:**

In this mode, VinIp/n and VinQp/n must be "short-circuited" at the ADC input; I channel input is sampled at the rising edge of CLK, and Q channel input is sampled at the falling edge of CLK; I Channel output delay 27.5 Cycles, Q channel output delay 28 Cycles;

Data is output on both edges of DCLK, the time sequence is DQ, DI (FDCLK = 1/2 FS)

Page 17 of 26

E-mail: sales @ cdcwtec.com Website:www.cdcwtec.com

Figure 9.3 CW12D1800 data timing in 1:2 Demux Non-DES

**Description:**

I channel input is sampled on the rising edge of

CLK; I channel output is delayed by 27.5 cycles;

Data is output on both edges of DCLK, the time sequence is DId, DI (FDCLK = 1/4 FS)

#### **Description:**

Figure 9.4 CW12D1800 Data Timing in 1:4 Demux DES Mode

In this mode, VinIp/n and VinQp/n must be "shorted" at the ADCinput; I channel input is sampled at the rising edge of CLK, and Q channel input is sampled at the falling edge of CLK; I channel output delay is 27.5 cycles, Q channel output delay is 28 cycles;

Data is output at both edges of DCLK, the time sequence is DQ, DI (FDCLK = 1/4 FS)

Page 18 of 26

E-mail: sales @ cdcwtec.com Website:www.cdcwtec.com

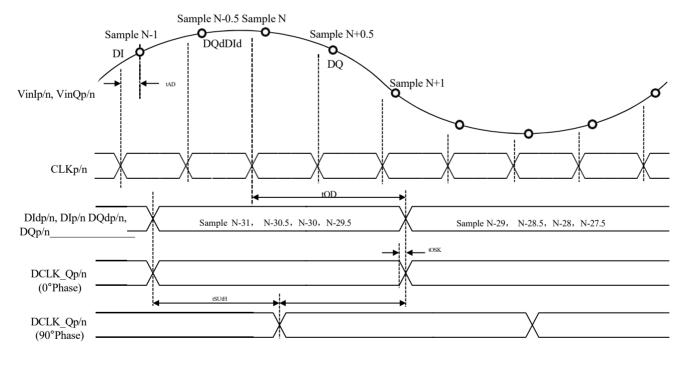

#### 9.2 Calibration Timing

Figure 9.5 Power-on Calibration and On-Command Calibration Timing

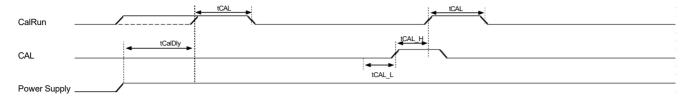

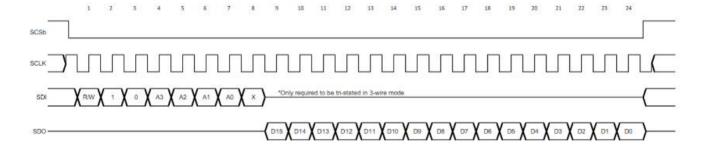

## 9.3 SPI Interface Timing

Figure 9.6 SPI write timing

Figure 9.7 SPI read timing

Table 9.1 SPI interface command and data field definition

| Bit  | Definition                | Description                                  |

|------|---------------------------|----------------------------------------------|

| 1    | Read/write<br>control bit | 1b: read operation 0b:<br>write operation    |

| 2~3  | Reserved                  | Default setting is 10b                       |

| 4~7  | Address bit<br>A[3:0]     | Register address, address order is MSB first |

| 8    | X                         | Reserved                                     |

| 9~24 | Data bit<br>D[15:0]       | Data is written to or read from the register |

Page 19 of 26

ChengduCuiweiElectronicCo., LTD Address:No 5,Gaopeng East Road, Gaoxin District, Chengdu, China E-mail: sales @ cdcwtec.com Website:www.cdcwtec.com

#

Figure 10.1 CW12D1800 package outline

SIDE VILW

| Table 10.1 CW12D1800:    | package outline dimensions  |

|--------------------------|-----------------------------|

| 1 auto 10.1 C W 12D 1000 | package outline unitensions |

TOP VILW

| Dimension symbol |         | Unit: mn | n       |

|------------------|---------|----------|---------|

|                  | Minimum | Typical  | Maximum |

|                  |         |          |         |

|                  |         |          |         |

| A                | 1.56    | 1.66     | 1.76    |

| A1               | 0.32    | 0.36     | 0.40    |

| A2               | -       | 0.7      | -       |

| A3               | 0.55    | 0.6      | 0.65    |

| D                | -       | 27.0     | -       |

| Е                | -       | 27.0     | -       |

| D1               | -       | 24.13    | -       |

| E1               | -       | 24.13    | -       |

| e                | -       | 1.27     | -       |

| ь                | 0.71    | 0.76     | 0.81    |

BOTTEM VIEW

## 11 Multi-chip synchronization function

CW12D1800 has two functions for synchronizing multiple ADC chips (AutoSync and DCLK Reset). The AutoSync function has two working modes: master-slave and full-slave. It is recommended to use the full-slave mode, use all CW12D1800 as Slave ADC, and use the clock board to provide the synchronous clock RCLK (CLK/16) to drive the RCLKp/RCLKn of each CW12D1800 through the equal length line to achieve synchronization of multiple CW12D1800. The DCLK Reset function is consistent with AutoSync, but has stricter requirements on the timing of use, so it is not recommended to use this function for multi-chip synchronization. The default configuration of CW12D1800 does not enable this function.

When using the AutoSync function for multi-chip synchronization, it is recommended to use the full-slave mode, use all CW12D1800 as Slave ADC, and use the clock board to provide the synchronous clock RCLK (CLK/16) to drive the RCLKp/RCLKn of each CW12D1800 through the equal length line to achieve synchronization of multiple CW12D1800. In order to synchronize the DCLK (including data) of multiple ADCs, all DCLKs must be in phase. Since the DCLK of CW12D1800 is generated by the RCLK inside the chip and retimed by the master clock CLK, the CLK signals of the synchronized ADCs must be in phase, that is, the master clock CLK arrives at the CW12D1800 at the same time. The enabling of the AutoSync function must be configured through the control register.

The figure below shows an example of synchronization of two Slave ADCs, where DCLKI and DCLKQ are not distinguished and are both represented by DCLK.

Figure 11.1 CW12D1800 AutoSync function connection

example If the AutoSync and DCLK Reset functions are not used, it

is recommended to connect unused PINs according to the table below.

Table 11.1 Recommendations for port connections when the AutoSync and DCLK Reset functions are not used

Page 21 of 26

ChengduCuiweiElectronicCo., LTD

Address:No 5,Gaopeng East Road, Gaoxin District, Chengdu, China

E-mail: sales @ cdcwtec.com

Website:www.cdcwtec.com

| port            | Connection suggestions               |

|-----------------|--------------------------------------|

| RCLKp/RCLKn     | Floating                             |

| RCOUT1p/RCOUT1n | Floating                             |

| RCOUT2p/RCOUT2n | Floating                             |

| DCLK_RST+       | Connect to GND<br>via a 1kΩ resistor |

| DCLK_RST-       | Connect to VA via<br>1kΩ resistor    |

# 12 Register list

Configuration Register 1

| Addr: 01 | n (0000b)                                    |                  |                               |           |           |           |          |           |            |            |            |           |            |          | POR                | c state | :: 200 |

|----------|----------------------------------------------|------------------|-------------------------------|-----------|-----------|-----------|----------|-----------|------------|------------|------------|-----------|------------|----------|--------------------|---------|--------|

| Bit      | 15                                           | 14               | 13                            | 12        | 11        | 10        | 9        | 8         | 7          | 6          | 5          | 4         | 3          | 2        |                    | 1       | 0      |

| Name     | CAL                                          | DPS              | OVS                           | TPM       | PDI       | PDQ       | Res      | Res       | DES        | Res        | Res        | SC        |            |          | Res                |         |        |

| POR      | 0                                            | 0                | 1                             | 0         | 0         | 0         | 0        | 0         | 0          | 0          | 0          | 0         | 0          | 0        | (                  | 0       | 0      |

|          | CAL, ca                                      | alibratio        | n enable                      | bit       |           |           |          |           |            |            |            |           |            |          |                    |         |        |

| Bit 15   | Setting                                      | CAL=1            | will trig                     | ger a coi | rection 1 | orocess.  | Since th | is contro | l bit wil  | l not be   | automatio  | cally cle | ared, wl   | nen the  | user t             | rigge   | rs     |

|          | _                                            |                  | .=0 must                      | _         |           |           |          |           |            |            |            | 3         |            |          |                    | 22      |        |

|          |                                              |                  |                               |           |           |           | the con  | rection p | rocess, w  | hich is    | functiona  | llv a "oı | " relatio  | onship,  | and h              | as no   |        |

|          |                                              |                  | ment bet                      |           |           |           |          | 1         | ,          |            |            | ,         |            | 1,       |                    |         |        |

|          |                                              |                  | e differe                     |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          |                                              |                  | he DDR                        |           |           | hase rela | tionship | is 0°     |            |            |            |           |            |          |                    |         |        |

| Bit 14   | When D                                       | )PS=1, tl        | he DDR                        | Data-to-l | OCLK p    | hase rela | tionship | is        |            |            |            |           |            |          |                    |         |        |

|          | 90°                                          | <b>D</b>         | 1 41                          | 1 1 2 42  |           | 11.1 1    |          | . DDI     | 2.00       | 1          |            |           |            |          |                    |         |        |

|          |                                              |                  | mode, thi                     |           |           | and and   | is aiway | 's in DDI | K U moc    | ie.        |            |           |            |          |                    |         |        |

|          |                                              |                  |                               |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

| Bit 13   | When OVS=0, the output voltage is 0.8V. When |                  |                               |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          | OVS=1, the output                            |                  |                               |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          |                                              | voltage is 1.2V. |                               |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          | This con                                     | ntrol bit i      | is the LV                     | DS outp   | ut pin (D | ATA, O    | R and D  | CLK), aı  | nd differe | ent voltag | ges are se | lected    |            |          |                    |         |        |

|          | TPM, te                                      | st mode          | enable b                      | it        |           |           |          |           |            |            |            |           |            |          |                    |         |        |

| Bit 12   | When T                                       | PM=0, 1          | normal w                      | orking n  | node      |           |          |           |            |            |            |           |            |          |                    |         |        |

|          |                                              |                  |                               |           |           | pin (Dig  | ital DAT | (A, OR)   | will cont  | inuously   | output a   | fixed dig | gital patt | ern      |                    |         |        |

|          |                                              |                  | ower-of                       |           | oit       |           |          |           |            |            |            |           |            |          |                    |         |        |

| Bit 11   |                                              |                  | ne I chan                     |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

| DII 11   |                                              |                  | g mode V                      |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          |                                              |                  | annel is                      |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          |                                              |                  | ing mod                       |           | ore       |           |          |           |            |            |            |           |            |          |                    |         |        |

|          | channel                                      | will be          | in powe                       | r-off mo  | de        | function  | olly "O  | R" relate | d Ac       | long       | s any sigr | ol ic     | volid (    | high lev | اء (امر            | ha I    |        |

|          |                                              |                  | power-o                       |           |           | Tancuo    | iany O   | ix iciaic | u. As      | rong as    | any orgi   | 161 15    | vanu (     | mgn ic   | v C1 <i>j</i> , ti | 110 1   |        |

|          | ` `                                          |                  | the Q ch                      |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

| Bit 10   |                                              |                  | g mode V                      |           | 111       |           |          |           |            |            |            |           |            |          |                    |         |        |

|          |                                              | _                | channel i                     |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          | -                                            |                  |                               |           |           |           |          |           |            |            |            |           |            |          |                    |         |        |

|          | This con                                     | ntrol bit        | ing mod<br>and the<br>in powe | PDQ pin   |           | function  | nally "O | R" relate | ed. As     | long as    | s any sigr | nal is    | valid (    | high lev | vel), tl           | he Q    |        |

| Addr: 0h | (0000b)                                                                                                                                                                                                                   |           |           |                       |          |     |     |     |     |     |     |    |   |     | POR stat | e: 2000h |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------------------|----------|-----|-----|-----|-----|-----|-----|----|---|-----|----------|----------|--|--|--|

| Bit      | 15                                                                                                                                                                                                                        | 14        | 13        | 12                    | 11       | 10  | 9   | 8   | 7   | 6   | 5   | 4  | 3 | 2   | 1        | 0        |  |  |  |

| Name     | CAL                                                                                                                                                                                                                       | DPS       | OVS       | TPM                   | PDI      | PDQ | Res | Res | DES | Res | Res | SC |   | Res |          |          |  |  |  |

| POR      | 0                                                                                                                                                                                                                         | 0         | 1         | 0                     | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0 | 0   | 0        | 0        |  |  |  |

| Bit 9    | Reserve                                                                                                                                                                                                                   | ed        |           |                       |          |     |     |     |     |     |     |    |   |     |          |          |  |  |  |

| Bit 8    | Reserved                                                                                                                                                                                                                  |           |           |                       |          |     |     |     |     |     |     |    |   |     |          |          |  |  |  |